Managing noise in the signal chain, Part 3: Select the best data converter for your noise budget - EDN

The Easy Steps to Calculate Sampling Clock Jitter for Isolated Precision High Speed DAQs | Analog Devices

Sensors | Free Full-Text | An Enhanced Technique for Ultrasonic Flow Metering Featuring Very Low Jitter and Offset

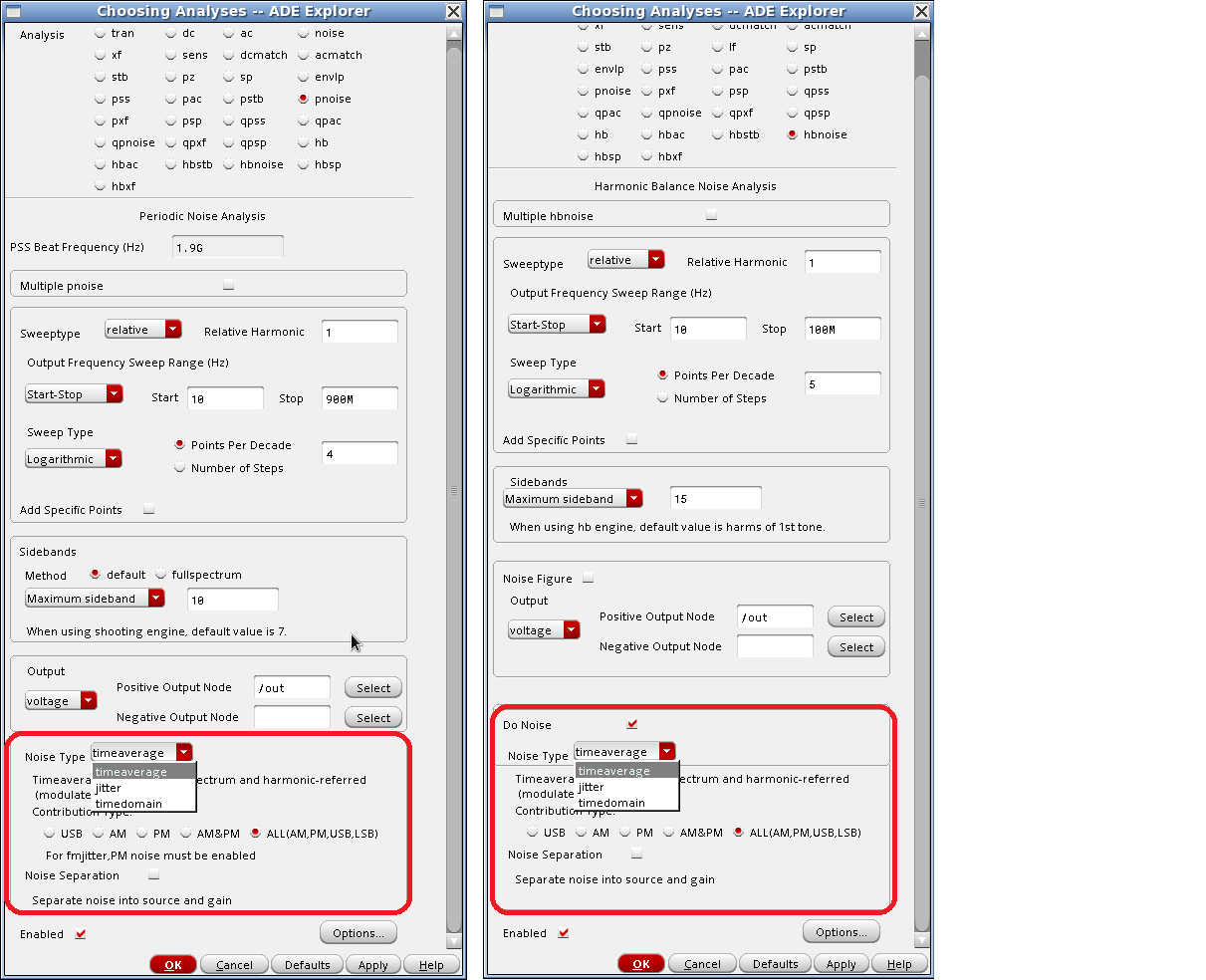

Noise Simulation in Spectre RF Using Improved Pnoise/Hbnoise and Direct Plot Form Options - RF Engineering - Cadence Blogs - Cadence Community

Quantization Noise, Thermal Noise, Flicker Noise, Phase Noise, and Clock Jitter in VCO-ADCs | SpringerLink

Low-jitter differential clock driver circuits for high-performance high-resolution ADCs | Semantic Scholar

Total and data-dependent jitter versus phase pre-emphasis codes for the... | Download Scientific Diagram

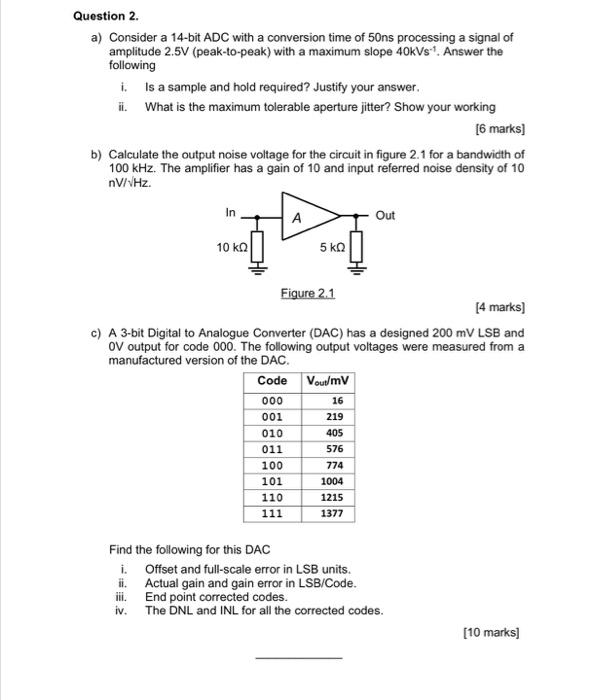

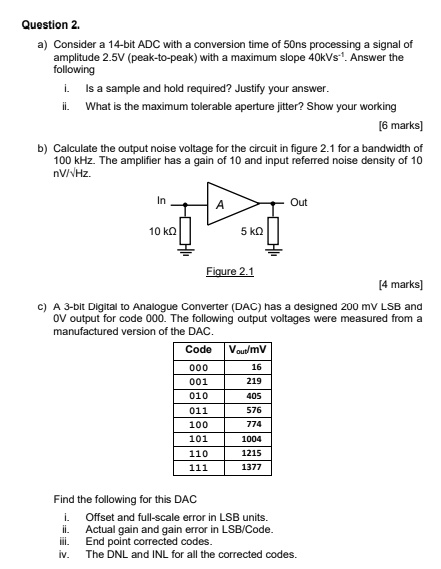

SOLVED: Question 2. a) Consider a 14-bit ADC with a conversion time of 50ns processing a signal of amplitude 2.5V (peak-to-peak) with a maximum slope 40kVs-1. Answer the following i. Is a

Relation between power per delay cell and DLL jitter, due to noise and... | Download Scientific Diagram